### DAQ for Fall 2018 Run

T. Lindner

### **RIUMF**

### **Overview**

DAQ Task list for 2018 run

- New gate control

- Add timing of gate valves

- Clean up sequencer controls

# **% TRIUMF**

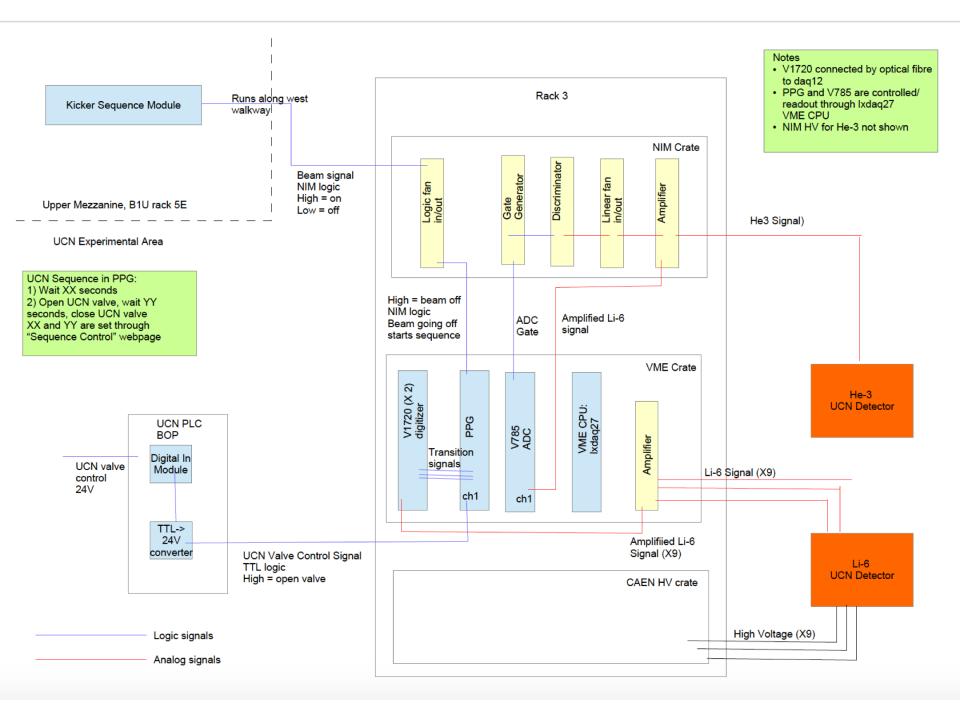

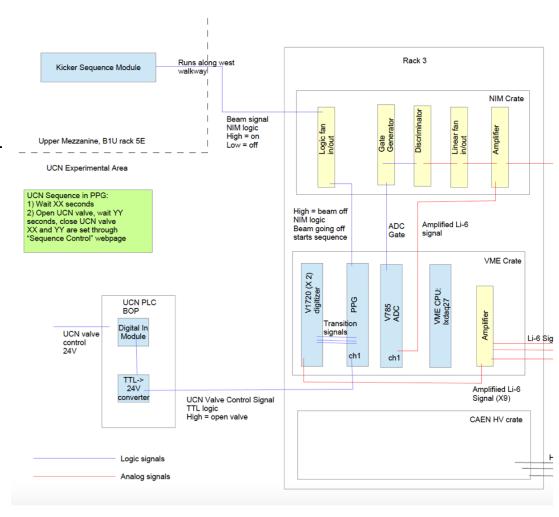

### **Valve Control**

- UCN Valve control (2017)

- Open and close initiated by VME sequencer card.

- Control signal converted from TTL to 24V and fed into PLC

- Control signal copied and sent to Li-6 V1720

- Repeat for N more valves.

Need

- Cables between VME crate and PLC.

- New PLC code and wiring.

- Don't have enough extra channels in V1720 digitizer to handle extra valve control signals.

# **%TRIUMF**

### **Improved Timing Measurements**

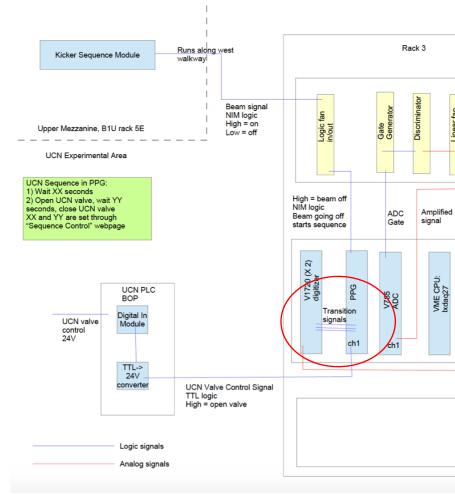

- There aren't enough spare channels in V1720 to record signals from 4 more gate valves.

- Need to add some other card to record when the other valves open/close. Options:

- MCS

- Chronobox (used by ALPHA-G)

- Would other card be synchronized to same clock as V1720? Hopefully.

- Otherwise injecting one gate signal into both V1720 and other card to synch them.

- We also will try to signal back from PLC that indicates exactly when the valves finish opening and closing. Could be useful to monitor that.

- Need to think about how to implement that.

# **%TRIUMF**

### **Improve Controls & Fix Bugs**

- Need to update the sequencer control page to add extra valves.

- How complicated, flexible to make the system for setting up valve sequences?

- Possibly simple sequences get set through webpage and complicated sequences get set through scripts.

- Did we write up list of DAQ problems from last year? I will need some reminding of the bugs that we wanted to fix.

- Also need better online monitoring, so we catch these problems at the time...

# **% TRIUMF**

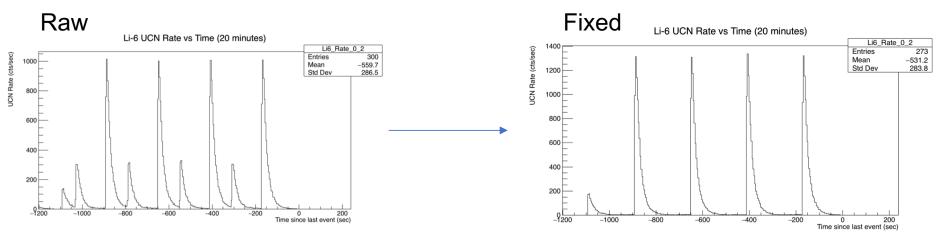

### V1720 Clock roll-overs

- Problem with shifted hits is caused by missing the 17s clock roll-over on V1720 digitizer

- In case Steve noted (run 814) missed 8 clock roll-overs for second V1720 board.

- Possible to fix for 2017 data... but need to figure out how to automate the fix.

- For 2018 run, should investigate again whether we can get the new V1720 firmware working that has longer timestamps.

# **% TRIUMF**

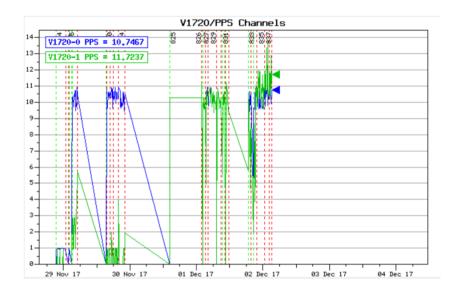

### V1720 Clock roll-overs

- Tried to avoid this problem by injecting a pulse-per-second signal into last channel of each V1720.

- But somehow this didn't work for second V1720 for this period.

- possibly related to recalibrating V1720 baselines.

- Somehow got fixed after Dec 1<sup>st</sup>, but can't find record of what was done.

- This problem is visible in history plots... need to add this to the hourly checks.

- Still not totally clear why the problem didn't affect all the runs in this period (Nov 29-31)

# **∂**TRIUMF

### **Backups**